-Karnaugh Maps

คือการลดรูปวงจร Logic Gate ที่ง่ายและรวดเร็วกว่ารูปแบบของ Boolean ซึ่งมีกฏ 3 ข้อในการทำดังนี้

- การวงเลข ที่ได้ในตาราง Output นั้นต้องวงกลมในแนวตั้งหรือแนวนอนเท่านั้น

- เลขที่อยู่ในวงนั้น จะต้องมีจำนวนของตัวเลข = 2ยกกำลัง(n)

- ในการวงเลขนั้นจะต้องไม่มีตัวเลขที่ต่างกันเลยในวงกลม (เลือกทำแบบ SOP วง1ต้องไม่มี0 , เลือกทำแบบ POS วง0ต้องไม่มี1)

ตัวอย่างกรณี K-map 2 input

ตัวอย่างกรณี K-map 3 input

ตัวอย่างกรณี K-map 4 input

ตัวอย่างกรณี K-map 5-6 input เราจะมองเห็น K-map เป็นภาพ 3 มิติ

จากตัวอย่าง!!! มีข้อสังเกตได้ว่า....

- ตาราง 2-4 input จะเป็นตาราง K-map แบบ 2 มิติ

- จำนวนช่องตารางในการสร้าง K-map จะเท่ากับจำนวน input ยกกำลัง 2

- การสร้างตาราง K-map นั้น เราจะเลือกใส่ input ใดมาก่อนหรือหลังก็ได้ เพียงแต่ต้องครบตามตาราง Truth Table ที่เราได้กำหนดไว้ในตอนแรก เช่น มี input = A,B,C จะเลือก AB,C หรือ A,BC หรือ AC,ฺB ก็ได้

- จำนวน input ตั้งแต่ 5 input ขึ้นไป ตาราง K-map จะเป็นแบบ 3 มิติ ในกรณีนี้หากทำการคำนวณจริงๆจะเห็นว่า จะมีความยุ่งยากในการสร้างตาราง K-map มากขึ้น ดังนั้น หากมี input มากกว่า 5-6 input ขึ้นไป แนะนำว่าควรใช้โปรแกรมในการคำนวณจะทำให้มีความผิดพลาดน้อยและรวดเร็วกว่ามาก

คุณสมบัติเพิ่มเติมของ K-map ที่ต้องทราบ!

--------------------------------------------------------------------------------------------------------------------------

--------------------------------------------------------------------------------------------------------------------------

- ตาราง K-map จากภาพตัวอย่างนั้น สามารถที่จะม้วนหรือจับมุมทั้ง 4 ด้านให้มาชนกันได้ นั้นหมายความว่า เราสามารถที่จะวงกลมตัวเลขที่เราม้วนแล้วมันมาติดกันได้ด้วย

- หากเป็นตาราง 5 input ขึ้นไป จะเป็นตารางแบบ 3 มิติ ซึ่งเราก็สามารถที่จะวงกลมตัวเลขที่เหมือนกัน ในตำแหน่งที่ตรงกัน ในแต่ละตารางได้อีกด้วย แต่อย่าลืม!!! ตัวเลขที่จะวงกลมนั้น ต้องมีจำนวนตัวเลขในวงกลม เท่ากับ 2ยกกำลัง(n)

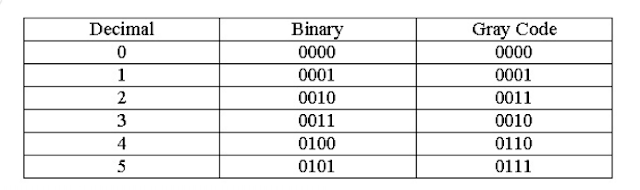

- ตัวเลข (00,01,11,10) ที่อยู่ข้างตารางนั้น เป็นตัวเลขแบบ GrayCode ไม่ใช่ BinaryCode

-เกร็ดความรู้เพิ่มเติม

GrayCode คือรหัสที่แต่ละค่าที่เปลี่ยนจะเปลี่ยนไปเพียง1บิตเสมอ เพื่อลดErrorในการส่งข้อมูล แต่ไม่เหมาะในการคำนวณ นิยมใช้กันมากในการนำมาประยุกต์ใช้กับการสร้างLogicต่างๆที่เกี่ยวข้องกับดิจิตอล

2.) ปัญหาที่พบ

- ยังไม่คล่องในการเขียน output ที่ดูจากการวง

- - ยิ่ง input มีเยอะ

ยิ่งต้องดูให้รอบคอบ อาจเกิดการผิดพลาดได้ง่าย